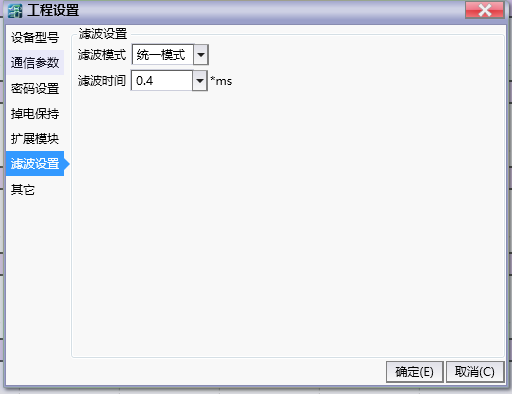

1. Set filter

1. Set filter

图1 Set filter

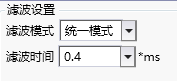

图2 filter setting

On this page, filtering settings can be made within the range of 0.20-51.20ms.

- There are three modes for filter setting: not enabled, unified mode and other modes.

When not enabled, software filtering of input signal X will not be enabled;

When the unified mode is selected, the filtering time can be configured, and the filtering parameters are applicable to all X input channels;

When selecting other options, the filtering time for each X input channel can be configured separately;

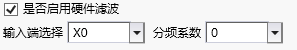

- For the multi pulse FGm series PLC, in addition to the filtering settings mentioned above, you can also choose whether to enable hardware filtering, but hardware filtering can only be configured for the first 16 X channels;

图3 set hardware filter

The frequency division coefficient is based on a sampling clock of 50MHz. In addition, the PLC defaults to continuously sampling the input signal after frequency division for 8 times to determine the unique high and low levels;

If the frequency division coefficient is selected as 2, it means that the 50MHz reference clock is first divided by two, and then the input signal is sampled at a sampling frequency of 25MHz. In addition, the internal default is that the level that needs to be continuously sampled 8 times is unique to determine its validity. If one of the 8 levels sampled continuously at 25MHz is different, it is considered an invalid level caused by interference. Therefore, this method can effectively suppress uncertain factors such as interference jitter;

Be careful when using this hardware filter. If the actual input signal frequency is high, do not set the division coefficient too high, otherwise the divided sampling clock will not be able to effectively sample the high-frequency input signal;

If the actual maximum counting frequency can reach 500KHz when using the high-speed counting function, the maximum configurable frequency division coefficient should be&# 60= 50MHz/(500KHz&# 42; 8&# 42; 2) ≈ 3, which means the maximum frequency division coefficient can be set to 2;